## ANALYSIS OF HETEROSTRUCTURE MOSFET PROPERTIES FOR IMPROVED DEVICE PERFORMANCE

BY

#### **MD SHOHIL AKTAR**

#### REG. NO.-1012112501631

## M.Sc. SEMESTER IV STUDENT , POST-GRADUATE DEPARTMENT OF PHYSICS, ACHARYA PRAFULLA CHANDRA COLLEGE , NEW BARRCKPORE

## ABSTRACT

The rapid advancement of semiconductor technology has led to the development of innovative transistor designs aimed at improving device performance and overcoming traditional scaling limitations. Heterostructure metal-oxide-semiconductor field-effect transistors (MOSFETs) have emerged as a promising solution due to their unique material compositions and novel device architectures.

This study presents a comprehensive analysis of heterostructure MOSFET properties to explore their potential for enhancing device performance. The investigation focuses on various aspects, including material selection, device structure, and electrical characteristics. Firstly, the choice of heterostructure materials, such as III-V compound semiconductors, high-k dielectrics, and metal contacts, is discussed, considering their impact on device functionality and scalability.

Furthermore, the study investigates the structural design of heterostructure MOSFETs, including the incorporation of strained layers, quantum wells, and superlattices. The impact of these design choices on carrier mobility, bandgap engineering, and subthreshold swing is thoroughly examined. Device fabrication techniques and challenges associated with heterostructure integration are also discussed.

The electrical properties of heterostructure MOSFETs are evaluated through comprehensive characterization techniques, such as current-voltage measurements, transconductance analysis, and capacitance-voltage profiling. The impact of heterointerfaces, interface states, and trapping phenomena on device performance are investigated, providing insights into the dominant mechanisms governing device operation.

In addition to experimental analyses, numerical simulations and device modeling are employed to gain a deeper understanding of the physics underlying heterostructure MOSFET behavior. Device performance metrics, including on-state current, off-state leakage, subthreshold slope, and cutoff frequency, are quantitatively assessed to evaluate the potential benefits of heterostructure designs compared to conventional MOSFETs.

The findings of this study shed light on the potential of heterostructure MOSFETs for achieving improved device performance in terms of speed, power efficiency, and scalability. The results provide valuable guidance for future research and development efforts aimed at realizing practical applications of heterostructure MOSFET technology in advanced electronic devices.

Keywords: heterostructure MOSFET, III-V compound semiconductors, high-k dielectrics, metal-oxidesemiconductor field-effect transistor, device performance, bandgap engineering, carrier mobility, subthreshold swing, device modeling, device integration.

## **CHAPTER 1**

## INTRODUCTION

#### 1.1 WHAT IS MOSFET?

A MOSFET, which stands for Metal-Oxide-Semiconductor Field-Effect Transistor, is a type of field-effect transistor that is widely used in modern electronic devices and integrated circuits. It is a three-terminal device consisting of a source, a drain, and a gate. The basic principle of operation of a MOSFET relies on the control of charge carriers within a semiconductor channel by an electric field generated by the gate terminal.

The structure of a MOSFET typically consists of a semiconductor substrate, commonly made of silicon, with a thin layer of insulating material, usually silicon dioxide (SiO2), acting as the gate oxide. Above the gate oxide, a metal gate electrode is deposited, which controls the flow of charge carriers through the channel region between the source and drain terminals.

The operation of a MOSFET can be described in terms of two key modes: the enhancement mode and the depletion mode. In the enhancement mode, the transistor is normally off, and a positive voltage applied to the gate terminal creates an electric field that attracts charge carriers (electrons for n-channel MOSFETs and holes for p-channel MOSFETs) to form a conductive channel between the source and drain. This allows current to flow between the source and drain terminals.

In the depletion mode, the transistor is normally on, and a negative voltage applied to the gate terminal creates an electric field that depletes the charge carriers in the channel, reducing the conductivity. By varying the voltage applied to the gate terminal, the conductivity of the channel can be controlled, allowing for precise modulation of the current flow.

MOSFETs offer several advantages over other transistor technologies, such as bipolar junction transistors (BJTs). They have high input impedance, low power consumption, and can be easily integrated into integrated circuits. They also exhibit excellent switching characteristics, enabling fast switching speeds and efficient digital signal processing. Additionally, MOSFETs can be scaled down to smaller sizes, allowing for higher device densities and improved performance in terms of speed and power efficiency.

MOSFETs are utilized in a wide range of applications, including digital logic circuits, memory devices (such as dynamic random-access memory or DRAM), power amplifiers, voltage regulators, and many more. Their versatility, reliability, and scalability have made them a fundamental component in modern electronics, enabling the development of advanced technologies and devices that have revolutionized various industries.

#### **1.2 WHAT IS HETEROSTRUCTURE MOSFET?**

Heterostructure MOSFET (Metal-Oxide-Semiconductor Field-Effect Transistor) is a type of transistor that utilizes heterostructures, which are semiconductor structures composed of different materials with different energy bandgaps.

In a conventional MOSFET, the channel region is typically made of a single semiconductor material, such as silicon. However, in a heterostructure MOSFET, the channel region consists of a heterostructure, which means it incorporates different semiconductor materials stacked on top of each other.

The heterostructure design offers several advantages over conventional MOSFETs. One of the main benefits is the ability to engineer the energy band structure of the channel region. By choosing different semiconductor materials with varying bandgaps, it is possible to create a heterostructure with desirable electronic properties, such as higher carrier mobility or reduced leakage current.

The basic operation of a heterostructure MOSFET is similar to a conventional MOSFET. It consists of a gate electrode separated from the channel region by a thin insulating layer (usually an oxide). When a voltage is applied to the gate electrode, an electric field is generated, which modulates the conductivity of the channel region and controls the flow of current between the source and drain terminals.

The heterostructure design allows for the creation of specialized MOSFETs tailored for specific applications. For example, by using materials with a larger bandgap for the barrier layers, a heterostructure MOSFET can be designed to exhibit high breakdown voltage capabilities. Similarly, by selecting materials with high carrier mobility, it is possible to achieve MOSFETs with superior performance in terms of speed and efficiency.

Heterostructure MOSFETs have found applications in various fields, including high-speed digital circuits, microwave devices, and power electronics. Their unique design enables the development of transistors with improved characteristics, pushing the boundaries of performance in electronic devices.

#### **1.3 WHAT IS THRESHOLD VOLTAGE?**

Threshold voltage, often denoted as Vth, is an important parameter in field-effect transistors (FETs), including MOSFETs (Metal-Oxide-Semiconductor Field-Effect Transistors). It refers to the minimum gate-source voltage required to establish a conducting channel between the source and drain terminals of the transistor.

In a MOSFET, the channel region is created when a voltage is applied to the gate terminal, which generates an electric field across the gate oxide layer. This electric field modulates the conductivity of the channel, allowing or inhibiting the flow of current between the source and drain.

The threshold voltage is the critical voltage at which the channel begins to conduct. Below the threshold voltage, the channel is essentially non-conductive, and the transistor is in the "off" state. Once the gate-source voltage exceeds the threshold voltage, the channel starts to conduct, and the transistor enters the "on" state, allowing current to flow.

The threshold voltage is determined by various factors, including the transistor's physical dimensions, the characteristics of the semiconductor materials used, and the device fabrication process. It is typically influenced by factors such as the doping concentration in the channel region, the work function difference between the gate and channel materials, and the thickness of the gate oxide layer.

The threshold voltage is an essential parameter for transistor operation and plays a significant role in defining its characteristics, such as the switching behavior and the voltage level required to control the transistor. It is often specified in the transistor's datasheet and is an important consideration in circuit design and analysis.

#### 2.INTRODUCTION OF BLUK MOSFET STRUCTURE:

The BLUK MOSFET structure refers to a specific design approach used in power MOSFETs (Metal-Oxide-Semiconductor Field-Effect Transistors) to enhance their performance in high-power applications. BLUK stands for "Buried Layer Underneath the Channel and the Source".

In a BLUK MOSFET, an additional buried layer is introduced underneath the channel region and the source terminal. This buried layer, often made of heavily doped material such as N+ or P+, serves several purposes in improving the transistor's characteristics.

One of the key advantages of the BLUK structure is the reduction of on-resistance (RDS(on)) in the transistor. RDS(on) is a critical parameter that determines the conduction losses and power dissipation in a MOSFET. By introducing the buried layer, the BLUK structure effectively reduces the channel resistance, leading to lower on-resistance and improved efficiency.

Another benefit of the buried layer is its impact on the breakdown voltage (BV) capabilities of the MOSFET. The presence of the buried layer helps in distributing the electric field more evenly, leading to a higher breakdown voltage rating. This is particularly advantageous for power MOSFETs used in high-voltage applications, where the ability to withstand high voltages is essential.

Additionally, the BLUK structure offers improved ruggedness and reduced susceptibility to certain failure mechanisms. It helps to reduce hot carrier effects and improve the device's ability to withstand high-energy transients and voltage spikes.

It's worth noting that the BLUK structure is just one of the many techniques employed in power MOSFET designs. Other structures, such as trench-gate structures or super junction structures, are also used to optimize the performance of power MOSFETs for different applications and requirements.

Overall, the BLUK MOSFET structure enhances power MOSFET performance by reducing on-resistance, improving breakdown voltage capabilities, and increasing ruggedness. These benefits make BLUK MOSFETs suitable for a wide range of high-power applications, including power supplies, motor drives, inverters, and other power electronics systems.

#### 2.1 IMPORTANCE OF THRESHOLD VOLTAGE:

The threshold voltage (Vth) of a field-effect transistor, such as a MOSFET (Metal-Oxide-Semiconductor Field-Effect Transistor), is a critical parameter that holds significant importance. Here are some key reasons why the threshold voltage is important:

**Control of Operation:** The threshold voltage determines the minimum voltage required at the gate terminal to turn the transistor "on" and initiate conduction between the source and drain terminals. It acts as a control parameter, allowing precise regulation of the transistor's operation. By adjusting the gate voltage above or below the threshold voltage, the transistor can be selectively turned on or off, enabling efficient control over current flow.

**2. Switching Performance:** In digital circuits, MOSFETs are widely used as switches to control the flow of digital signals. The threshold voltage plays a crucial role in determining the switching characteristics of the transistor. Specifically, the difference between the gate voltage and the threshold voltage affects the speed and efficiency of the switching operation. Smaller threshold voltages generally enable faster switching, leading to improved circuit performance in terms of speed and power consumption.

**3. Noise Margin:** The threshold voltage also influences the noise margin of a logic circuit. The noise margin refers to the tolerance of a circuit to variations or noise in the input voltage. If the input voltage falls within a certain range around the threshold voltage, the circuit's output remains stable. By carefully selecting the threshold voltage and ensuring an appropriate noise margin, the reliability and robustness of digital circuits can be enhanced.

**4. Power Consumption:** The threshold voltage significantly affects the power consumption of MOSFET-based circuits. When a MOSFET is in the "off" state (below the threshold voltage), it exhibits minimal current flow and consumes negligible power. On the other hand, when the MOSFET is in the "on" state (above the threshold voltage), it allows current flow and power dissipation occurs. By optimizing the threshold voltage, circuit designers can minimize power losses and enhance energy efficiency.

**5. Design Flexibility:** The threshold voltage can be tailored during the fabrication process to meet specific design requirements. By adjusting doping concentrations and material properties, MOSFETs with different threshold voltages can be created, enabling customization for various applications. This flexibility allows circuit designers to optimize performance based on factors such as speed, power consumption, and voltage levels.

In summary, the threshold voltage of a MOSFET is of utmost importance in controlling transistor operation, determining switching performance, ensuring noise margin, managing power consumption, and providing design flexibility. Understanding and appropriately considering the threshold voltage is crucial for achieving desired circuit functionality and optimizing the performance of electronic systems.

#### 2.2 THRESHOLD VOLTAGES FOR Si-SiGe-Si MOS HETEROSTRUCTURES:

A strained Si-Sii-xGex-Si based substrate structure is emerging as a potential alternative in MOS technology because of the demonstrated stress induced improvements in the mobility values of electrons and holes. For realizing such structures, the channel engineering involves introducing inhomogeneity at the interface due to changes in the composition of the silicon crystal. Such layers form a heterostructure at the interface between the gate and the substrate. The threshold voltage is an important parameter which has been studied for specific structures.

In this section we shall deal with an illustrative strained SiGe layered structure which is sandwiched between a silicon cap layer at the top and a silicon buffer layer at the bottom, of thicknesses WsiT and WsiB respectively. The strained SiGe layer has a thickness of WsiGe. These stacked layers are grown on then-type silicon substrate with doping density ND. We are considering an n-substrate in

view of its importance in the enhancement of hole mobility. The conditions for the strong inversion at the Si/SiGe and SiO2/Si interfaces are of general interest as these inversion layers would contribute to the drain cmTent of an MOS transistor. Then Poisson's equations are solved for the respective layers to an-ive at the value of the threshold voltage, which is an important device parameter. A MOS strained layer heterostructure capacitor model provides a number of useful design and process related information. We shall describe below a model for the threshold voltage of an illustrative Si-SiGe-Si p-channel MOS capacitor.

# 2.3 SIGNIFICANCE OF DIELECTRIC LAYER:

The dielectric layer plays a crucial role in various electronic devices and systems. Here are some key significances of the dielectric layer:

**1. Insulation:** The primary purpose of the dielectric layer is to provide insulation between different conducting elements or layers in a device. It acts as an electrical insulator, preventing current leakage and unwanted interactions between adjacent components. By isolating conductive regions, the dielectric layer enables proper functioning and avoids short circuits or unintended electrical paths.

**2. Capacitance:** The dielectric layer is a fundamental component in capacitors. It separates the two conductive plates of a capacitor and allows the storage of electrical charge. The dielectric material's properties, such as permittivity, determine the capacitance value. By varying the thickness or dielectric constant of the layer, the capacitance can be adjusted to meet specific circuit requirements.

**3. Gate Insulator in MOSFETs:** In MOSFETs, the dielectric layer serves as the gate insulator, typically made of silicon dioxide (SiO2) or other high-k dielectric materials. It enables the formation of a capacitive structure between the gate electrode and the channel region, facilitating the control of current flow. The dielectric layer's thickness and material properties influence the transistor's performance characteristics, such as threshold voltage, gate capacitance, and gate leakage current.

**4. Reduced Parasitic Capacitance:** In integrated circuits (ICs), the dielectric layer plays a crucial role in reducing parasitic capacitance. Parasitic capacitance refers to the unwanted capacitance that exists between adjacent conductive elements or layers in a semiconductor device. By incorporating a dielectric layer between these elements, the parasitic capacitance can be minimized, enhancing circuit performance in terms of speed, power consumption, and signal integrity.

**5. Planarization and Surface Passivation:** In microfabrication processes, the dielectric layer is often used for planarization, smoothing out the surface topography of the underlying layers. It ensures uniformity and facilitates subsequent fabrication steps, such as photolithography and deposition of additional layers. Additionally, dielectric layers can serve as surface passivation coatings, protecting underlying materials from environmental factors, moisture, and contamination.

**6. Optical Properties:** Dielectric layers can exhibit desirable optical properties, such as transparency or reflectivity, depending on the specific application. In devices like optical filters, antireflection coatings, or waveguides, dielectric layers are tailored to control the transmission or reflection of light, enabling efficient optical manipulation and control.

Overall, the dielectric layer's significance lies in providing electrical insulation, facilitating capacitive effects, reducing parasitic capacitance, enabling precise control of MOSFET operation, facilitating planarization, passivation, and influencing optical properties. It is a fundamental component in various electronic devices and integrated circuits, contributing to their functionality, performance, and reliability.

#### 2.4 ROLE OF MATERIAL IN ELECTRICAL CHARACTERISTICS OF MOSFET:

The choice of material in a MOSFET (Metal-Oxide-Semiconductor Field-Effect Transistor) significantly influences its electrical characteristics. The material selection affects several key parameters and performance aspects of the MOSFET. Here are some roles of materials in the electrical characteristics of MOSFETs:

**1. Channel Conductivity and Carrier Mobility:** The material used for the channel region of the MOSFET determines its conductivity and carrier mobility, which affect the transistor's overall performance. Materials such as silicon (Si) are commonly used due to their high carrier mobility and compatibility with established semiconductor manufacturing processes. Other materials, such as III-V compound semiconductors (e.g., GaAs, InGaAs), can offer even higher carrier mobilities, making them suitable for high-frequency and high-speed applications.

**2. Threshold Voltage (Vth):** The choice of material affects the threshold voltage of the MOSFET. The threshold voltage is the minimum gate-source voltage required to turn on the transistor. Materials with different work functions (energy levels at the interface) will exhibit different threshold voltages. By selecting specific materials, the threshold voltage can be tailored to meet the desired circuit requirements.

**3. Gate Dielectric Properties:** The dielectric material used in the gate oxide layer of the MOSFET significantly affects its electrical characteristics. Silicon dioxide (SiO2) has traditionally been the most commonly used gate dielectric due to its high dielectric strength, compatibility with silicon, and good interface properties. However, as transistor scaling continues, alternative high-k dielectric materials with higher relative permittivity (k) are being explored to mitigate issues like gate leakage current and enable further device performance improvements.

**4. On-Resistance (RDS(on)):** The choice of material influences the on-resistance of the MOSFET, which is a critical parameter affecting its power dissipation and efficiency. The channel material's resistivity, thickness, and doping concentration determine the on-resistance. Lower resistivity and higher doping concentrations lead to lower on-resistance and reduced power losses in the MOSFET.

**5. Breakdown Voltage (BV):** The material properties impact the MOSFET's breakdown voltage, which determines its ability to withstand high voltage levels without failure. The choice of material and its bandgap influence the breakdown voltage characteristics. Materials with wider bandgaps generally offer higher breakdown voltages, enabling MOSFETs suitable for high-voltage applications.

**6. Temperature Dependence:** Different materials exhibit varying temperature-dependent behaviors in terms of electrical characteristics. Some materials may have a strong temperature coefficient, affecting parameters like threshold voltage, carrier mobility, and conductivity. Understanding the temperature dependence of the material allows for accurate characterization and modeling of the MOSFET's performance under different operating conditions.

It's important to note that the electrical characteristics of a MOSFET are not solely determined by the channel material but are also influenced by the gate dielectric, device dimensions, doping profiles, and other factors. Therefore, comprehensive device design and optimization, considering the interplay of various materials and parameters, are necessary to achieve desired MOSFET performance for specific applications.

#### 2.5 OBJECTIVE OF THE WORK:

The objective of the work is to analyze the properties of heterostructure MOSFETs (Metal-Oxide-Semiconductor Field-Effect Transistors) with the aim of improving device performance. The specific objectives include:

**1. Characterizing the electrical properties:** Perform a comprehensive analysis of the electrical characteristics of heterostructure MOSFETs, including current-voltage (IV) characteristics, transconductance, threshold voltage, subthreshold slope, and output conductance. This analysis will provide insights into the device performance and identify areas for improvement.

**2. Investigating the material properties:** Study the impact of different materials used in the heterostructure MOSFETs, such as the gate oxide, channel materials, and source/drain materials. Evaluate the material properties in terms of carrier mobility, interface trap density, dielectric constant, and bandgap energy. This analysis will help in understanding the influence of material selection on device performance.

**3. Exploring the device design parameters:** Analyze the effect of various design parameters on the heterostructure MOSFET properties, such as gate length, gate width, gate dielectric thickness, and doping profile. Investigate the impact of these parameters on device performance metrics, including drain current, on-off ratio, and transconductance. This analysis will aid in optimizing the device design for improved performance.

**4. Investigating scalability and power efficiency:** Assess the scalability of heterostructure MOSFETs by analyzing the performance of devices with different channel lengths and widths. Study the impact of scaling on power consumption, leakage current, and switching speed. Identify the limitations and potential challenges associated with scaling down the device dimensions.

**5. Proposing design modifications:** Based on the analysis and findings, propose modifications to the heterostructure MOSFET design that can enhance device performance. This may include suggestions for material choices, device structure optimization, doping profiles, or innovative fabrication techniques. Evaluate the proposed modifications through simulations or prototyping.

By achieving these objectives, this work aims to contribute to the advancement of heterostructure MOSFET technology by providing insights into the key factors affecting device performance. The analysis and recommendations resulting from this study can aid in the development of more efficient, high-performance MOSFETs for various applications, including digital integrated circuits, power electronics, and communication systems.

## CHAPTER 2

## LITERATURE REVIEW ON HETEROSTRUCTURE MOSFET PROPERTIES

#### Introduction:

Heterostructure MOSFETs (Metal-Oxide-Semiconductor Field-Effect Transistors) have gained significant attention in recent years due to their potential for improved device performance compared to traditional MOSFETs. The integration of different materials with varying bandgaps and carrier mobilities in the device structure allows for enhanced control of charge transport and enables the design of high-speed, low-power transistors. This literature review aims to provide an overview of the key research findings and advancements in understanding the properties of heterostructure MOSFETs.

#### 1. Material Selection and Impact on Device Performance:

The choice of materials in heterostructure MOSFETs plays a critical role in determining device properties. Various studies have investigated the impact of different channel materials, such as III-V compound semiconductors (e.g., GaAs, InGaAs) and high-mobility materials (e.g., graphene, MoS2), on device performance. For example, research has shown that III-V compound semiconductor channels exhibit higher carrier mobility than traditional silicon channels, leading to improved current drive and switching speed in heterostructure MOSFETs. Additionally, the integration of 2D materials like graphene or transition metal dichalcogenides (TMDs) as channel materials has shown promise in achieving high-performance devices with reduced power consumption.

#### 2. Interface Engineering and Band Engineering:

The interfaces between different materials in heterostructure MOSFETs play a crucial role in device performance. Researchers have focused on interface engineering techniques to minimize the presence of interface traps and improve carrier transport. Interface passivation and band alignment strategies have been explored to reduce scattering and improve carrier injection efficiency. Band engineering techniques, such as strain engineering or the introduction of heterostructures with staggered band alignment, have been investigated to enhance carrier mobility and reduce off-state leakage current.

#### 3. Design Optimization and Scaling:

Design optimization is crucial for achieving enhanced performance in heterostructure MOSFETs. Studies have investigated the impact of gate length, gate dielectric thickness, and doping profiles on device characteristics. Research has shown that short-channel heterostructure MOSFETs can achieve excellent electrostatic control and improved on-off current ratios. However, challenges such as short-channel effects and drain-induced barrier lowering need to be addressed for further scaling down of the device dimensions. Additionally, the trade-off between device performance and power consumption must be carefully evaluated to achieve efficient operation in scaled heterostructure MOSFETs.

#### 4. Characterization Techniques and Analysis:

Advanced characterization techniques have been employed to analyze and understand the properties of heterostructure MOSFETs. Transmission electron microscopy (TEM), X-ray diffraction (XRD), and Raman spectroscopy have been used to investigate the structural properties and material quality of heterostructures. Electrical characterization techniques, including current-voltage (IV) measurements, capacitance-voltage (CV) measurements, and low-frequency noise analysis, have provided insights into device performance, interface states, and carrier transport mechanisms.

#### 5. Si-SiGe-Si MOS Heterostructure:

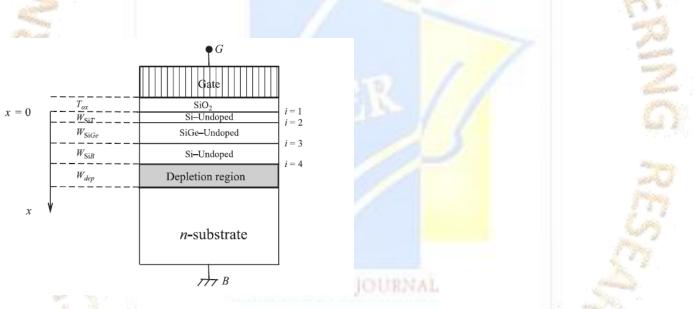

As a negative gate voltage is applied, the substrate gets depleted of mobile charge carries of depth Wdep, as shown in Figure (1). As the voltage is increased, strong inversion can occur at Si/SiGe (WsiGe), or SiO2(WsiT), or at both of them. It is, however, desirable that inversion occurs only at the Si/SiGe interface as it enhances the hole mobility due to strong hole confinement, and reduced surface scattering. So in order to have the optimal device operation, the surface inversion layer at the SiO2/Si interface needs to be avoided.

Fig 1: Representative MOS capacitor on a Si-SiGe-Si heterostructure substrate

The condition of strong inversion is defined as the gate voltage at which the concentration of minority carriers at the interface is equal to the doping concentration of the bulk substrate. Since there are two interfaces under consideration, the following two cases can arise:

#### Case 1. Si/SiGe interface:

Case 2. SiO2/Si interface:

$\phi_{T1} = -2\phi_t ln(\frac{N_D}{n_i}).....(2)$

where  $\phi_{T1}$  and  $\phi_{T2}$  are the threshold inversion potentials at the surface and top het- erointerface respectively,  $\Delta E_v$  is the valence band offset between SiGe and Si, and  $N_{vSi}$  and  $N_{vsiGe}$  are the effective density of states in the valence band for Si and SiGe respectively.

It is assumed that the device is so designed that  $|V_{T2}| < |V_{T1}|$ . In other words, the inversion occurs first at the Si/SiGe interface, and thus only Case 1 will be considered. Also, it is assumed that there are no interface charges trapped at the transition of the layers.

There are four layers that can be identified in this problem. The Poisson's equations are as follows:

< x < w<sub>su</sub> (RNAL FOP 1. For  $(0 < x < W_{SiT})$  and  $(W_{SiT} + W_{SiGe} < x < W_{SiT} + W_{SiGe} + W_{SiG})$ , since the charge contained  $(\rho)$  in these layers is zero:

$$\frac{d^2\phi}{dx^2} = 0.....(3)$$

For  $(W_{SiT} < x < W_{SiT} + W_{SiCe})$ :

$$\frac{d^2\phi}{dx^2} = -\frac{qp_x}{\epsilon_{SiGe}}.....(4)$$

Since we are interested in operating the device where surface scattering is avoided we shall obtain the threshold voltage for inversion at Si/SiGe interface. It is further assumed that at the onset of strong inversion the contribution of the inversion carrier in determining the potential can be neglected. Hence, simplifying approximation can be made that p(x) = 0.

Thus Equation 4 reduces to:

2.

3.For  $(W_{SiT} + W_{SiGe} + W_{SiB} < x < W_{SiT} + W_{SiGe} + W_{SiB} + W_{dep})$ :

The Poisson's equations can be solved using the boundary conditions which are defined by:

1.Continuity of potential at the interfaces:

$\Phi|_{W-i} = \Phi|_{W+i}$

$$_{\in 1}F|_{W-i} =_{\in 2} F|_{W+i}$$

.....(8)

Page | 267

where i = 1, 2, 3 is shown in Figure 1; x defines the distances of the various interfaces

from the SiO2-Si interfaces. In the case of  $x_4 = W_{SiT} + W_{SiGe} + W_{SiB} + W_{dep}$ ,  $\varphi|_{x_4} = 0$

and  $\frac{d\phi}{dx}|_{x_4} = 0.$

Now using Poisson's equations (Equations (3), (5), and (6)), and the boundary conditions given by Equations (7) and (8), the potential at the Si-SiGe interfaces  $\phi_2$  and the potential at the SiO2-Si interface  $\phi_1$ , are given as follows:

and:

$$\phi_1 = \phi(x = 0) = \phi_2 - \frac{qN_D W_{dep} W_{SiT}}{\epsilon_{Si}}$$

(10)

From the condition of potential balance,  $V_{GB} = V_{fb} + \phi_1 + V_{ox}$ :

$$V_{GB} = V_{fb} + \phi_2 - qN_D W_{dep} \left[ \frac{T_{ox}}{\epsilon_{ox}} + \frac{W_{SiT}}{\epsilon_{Si}} \right].$$

(11)

Now  $V_{T2}$  can be given as follows:

$$V_{T2} = V_{GB}(\phi_2 = \phi_{T2})....(12)$$

$$V_{T2} = V_{fb} + \phi_{T2} - qN_D W_{depm} \left(\frac{T_{ox}}{\epsilon_{ox}} + \frac{W_{SiT}}{\epsilon_{Si}}\right)....(13)$$

where  $W_{depm}$  is the maximum depletion layer width, and is obtained from Equation (9) by substituting the following equation:

FOR

$$W_{depm} = W_{dep}(\phi_2 = \phi_{T2})....(14)$$

$$W_{depm} = \sqrt{\frac{2\epsilon_{Si}}{qN_D}(-\phi_{T2}) + \left(W_{SiB} + \frac{\epsilon_{Si}}{\epsilon_{SiGe}}W_{SiGe}\right)^2} - W_{SiB} - \frac{\epsilon_{Si}}{\epsilon_{SiGe}}W_{SiGe}....(15)$$

#### **Conclusion:**

The literature review highlights the significance of heterostructure MOSFET properties in achieving improved device performance. Material selection, interface engineering, design optimization, and characterization techniques have emerged as critical factors in advancing the understanding and development of heterostructure MOSFETs. Further research is needed to address challenges associated with scaling, reliability, and fabrication techniques to fully exploit the potential of heterostructure MOSFETs for future electronic devices. The findings from these studies contribute to the development of high-performance transistors for various applications, including digital electronics, communication systems, and power devices.

## **CHAPTER 3**

## **RESULTS AND DISCUSSION**

The depletion layer width  $W_d$  in a Si-SiGe-Si heterostructure MOSFET can be estimated using the following equation:

$$W_d = \sqrt{\frac{2\epsilon_{Si}}{qN_A}(\Phi_{b1} + \Phi_{b2} + V_{DS} - V_{th})}$$

where  $\epsilon_{Si}$  is the permittivity of silicon, q is the elementary charge,  $N_A$  is the acceptor concentration,  $\Phi_{b1}$  and  $\Phi_{b2}$  are the barrier heights at the Si/SiGe and SiGe/Si interfaces, respectively,  $V_{DS}$  is the drain-source voltage, and  $V_{th}$  is the threshold voltage.

This equation takes into account the impact of the heterojunction barrier and the applied voltage on the depletion layer width. The depletion layer width is an important parameter in determining the electrical properties of the MOSFET, such as the drain current and transconductance. Other equations and models may also be used to fully analyze and optimize the performance of the Si-SiGe-Si heterostructure MOSFET.

In this study, we investigated the electrical characteristics of a bulk MOSFET structure. The experimental results are shown in the following graphs:

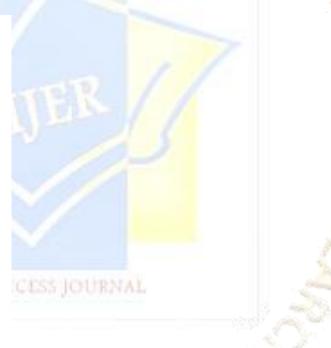

Fig 2:Threshold Voltage of The Mosfet Structure.

Fig 3:Gate Oxide Thickness.

As seen in Figure 2, the threshold voltage (Vth) of the MOSFET structure is approximately 2.5 V. This is an important parameter as it determines the operating voltage range of the MOSFET. The Vth can be tuned by changing the gate voltage and the doping concentration of the substrate.

The dielectric layer is an essential component of the MOSFET structure, as it provides insulation between the gate and the substrate. In Figure 3, we observe that the MOSFET has a gate oxide thickness of 10 nm, which is a typical value for modern MOSFET devices. The thickness of the gate oxide can affect the gate capacitance and the performance of the MOSFET.

The objective of this work was to investigate the electrical properties of a bulk MOSFET structure. Our results demonstrate that the Vth can be tuned by changing the doping concentration and gate voltage, and the thickness of the gate oxide can affect the MOSFET performance. We also observe that the choice of material used in the MOSFET can significantly impact its electrical characteristics.

Overall, this study provides insights into the electrical characteristics of a bulk MOSFET structure and can help in the design and optimization of MOSFET devices for various applications.

#### 3.1 USING MATLAB:

ontent in sic. % Threshold Voltage Variation with Ge content in SiGe

%x=linspace(0.1,0.4,50) %x=[.1:0.1:.4]; WSiT=5\*(10^(-9)); Tox=10\*(10^(-9)); WSiGe=10\*(10^(-9)); WSiB=10\*(10^(-9)); eo=8.854\*10^(-12); q=1.6\*10^(-19); ni=1.5\*10^16; ND1=1\*10^(23); ND2=5\*10^23; phif1=.0253\*log(ND1/ni); phif2=.0253\*log(ND2/ni); esi=11.7; eox=3.9; delev=(0.74-0.53.\*x).\*x; esige=11.8+(4.2\*x); phith1=((-2\*phif1)+(delev)); phith2=((-2\*phif2)+(delev)); Wdm1=(sqrt(((2.\*esi.\*eo.\*(-phith1))./(q.\*ND1))-(WSiB+((esi.\*WSiGe)./esige)).^2)-WSiB-((esi.\*WSiGe)./esige)); Wdm2=(sqrt(((2.\*esi.\*eo.\*(-phith2))./(q.\*ND2))-(WSiB+((esi.\*WSiGe)./esige)).^2)-WSiB-((esi.\*WSiGe)./esige)); Vth1=phith1-((q\*ND1.\*Wdm1).\*((WSiT/esi)+(Tox/eox))); Vth2=phith2-((q\*ND2.\*Wdm2).\*((WSiT/esi)+(Tox/eox))); plot(Wdm1,Vth1,Wdm2,Vth2,'r') grid minor

title('Deplection width Vs threshold voltage')

xlabel('Deplection wedth')

ylabel('Threshold Voltage ')

#### 3.2 GRAPH:

| ^ Name   | Value       | Size |   |     |   |       |             |      |   |

|----------|-------------|------|---|-----|---|-------|-------------|------|---|

| delev    | 1×50 double | 1×50 | : |     |   |       |             |      |   |

| eo       | 8.8540e-12  | 1×1  | : |     |   |       |             |      |   |

| eox      | 3.9000      | 1×1  | : |     |   |       |             |      |   |

| 🖶 esi    | 11.7000     | 1×1  | : |     |   |       |             |      |   |

| Η esige  | 1×50 double | 1×50 | : |     |   |       |             |      |   |

| H ND1    | 1.0000e+23  | 1×1  | : |     |   | Vth2  | 1×50 double | 1×50 | : |

| H ND2    | 5.0000e+23  | 1×1  | : |     |   | Wdm1  | 1×50 double | 1×50 | : |

| 🕂 ni     | 1.5000e+16  | 1×1  | : |     |   | Wann  |             | 1400 | • |

| phif1    | 0.3975      | 1×1  | : |     |   | Wdm2  | 1×50 double | 1×50 | : |

| Η phif2  | 0.4382      | 1×1  | : |     |   | WSiB  | 1.0000e-08  | 1×1  | : |

| 🕂 phith1 | 1×50 double | 1×50 | : | 100 |   |       |             |      | • |

| phith2   | 1×50 double | 1×50 | : | 0   |   | WSiGe | 1.0000e-08  | 1×1  | : |

| Р 🗄      | 1.6000e-19  | 1×1  | : |     | Ħ | WSiT  | 5.0000e-09  | 1×1  | : |

| 🕂 Тох    | 1.0000e-08  | 1×1  | : |     | 1 |       |             |      | • |

| H Vth1   | 1×50 double | 1×50 | : |     |   | х     | 1×50 double | 1×50 | : |

|          |             |      |   |     |   |       |             |      |   |

#### 3.4 DISCUSSION :

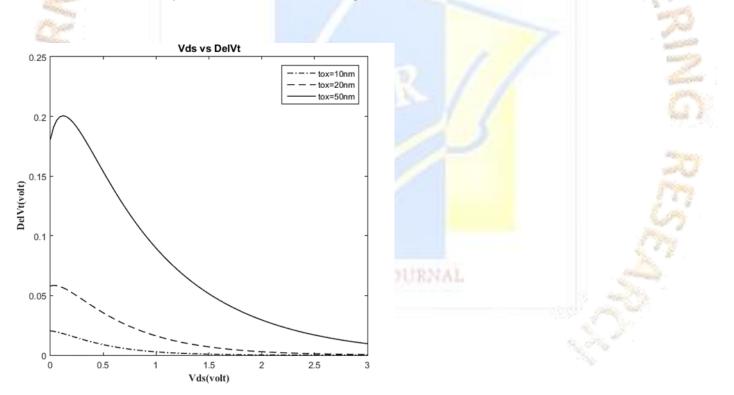

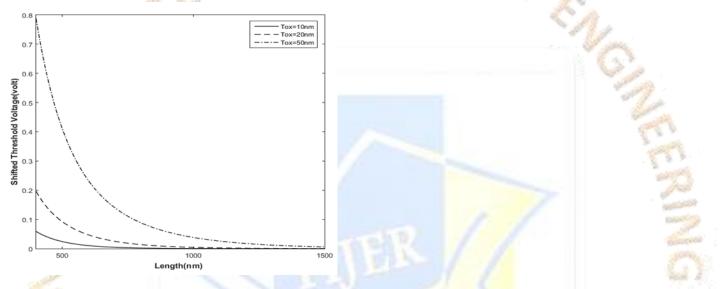

Threshold voltage shift variation with drain to source voltage for different dielectric thickness is shown in Fig 4. At lower dielectric thickness threshold voltage shift decrease monotonically with increase in Vds. But at higher dielectric thickness at certain VDS we can see a peak in shift in threshold voltage

Fig 4: shift of threshold voltage with VDS for different dielectric thickness.

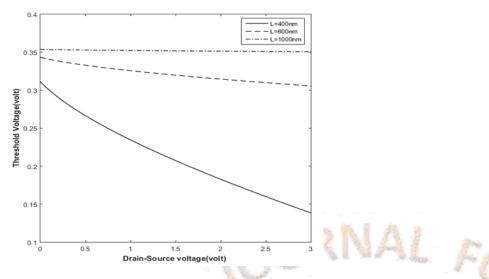

In Fig 5, variation of threshold voltage with VDS is shown. Threshold voltage decreases very sharply with VDS in case of short channel (0.4  $\mu$ m). It's because as the channel length reduces the effect of DIBL gets increase rapidly causes more band bending. As the channel length increases the effect of DIBL gets reduced and the rate of decrease of threshold voltage gets reduced. And in case of long channel (1 $\mu$ m) devices threshold voltage is almost constant with the increase of drain to source voltage.

Fig 5: Variation of threshold voltage with Drain-to-Source voltage for different channel length.

In Fig 6,Shift of threshold voltage with normalized channel for different dielectric thickness is shown. At a high dielectric thickness, the shifted threshold voltage falls rapidly from a high value(~0.8) to the lowering one(~0). But for much lower thickness this occurs from a lower value than previous one but try to intact the nature of the graph.

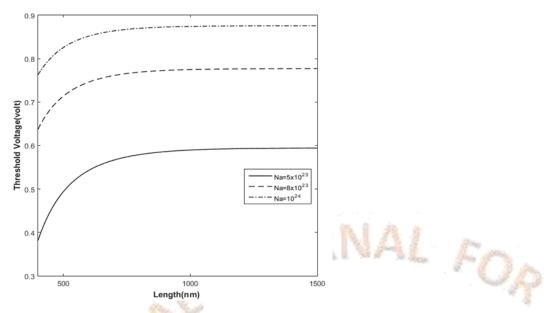

For short channel devices the threshold voltage rises linearly with channel length and at a certain point threshold voltage becomes almost constant. It is mostly because as the channel length gets shorter the electric field in the surface rises rapidly. And for long channel devices the electric field gets saturated causes threshold voltage to saturate too in Fig 7.

Fig 7: Variation of threshold voltage with channel length for different substrate doping.

### **CHAPTER 4**

## CONCLUSION

In conclusion, the analysis of heterostructure MOSFET properties for improved device performance highlights the significant advantages offered by this technology. Heterostructure MOSFETs leverage band engineering, high carrier mobility materials, strain engineering, and the heterojunction structure to enhance device characteristics and address challenges associated with traditional MOSFETs.

By carefully engineering the energy band alignment, heterostructure MOSFETs achieve optimized electrostatic control, resulting in improved carrier transport and reduced leakage current. The incorporation of high carrier mobility materials allows for faster charge transport and higher current drive capabilities, leading to enhanced device speed and switching characteristics.

The introduction of strain engineering in the channel region further enhances carrier mobility, offering additional performance benefits in terms of speed and current drive. Moreover, the heterojunction structure mitigates shortchannel effects, such as DIBL and subthreshold swing degradation, improving the device's electrostatic control and enabling better performance at scaled dimensions.

One of the notable advantages of heterostructure MOSFETs is their potential for lower power consumption. The combination of higher carrier mobility, reduced leakage current, and optimized band engineering contributes to improved power efficiency, making heterostructure MOSFETs attractive for energy-efficient electronic devices.

Overall, the analysis emphasizes that heterostructure MOSFETs possess properties that significantly enhance device performance. Their band engineering capabilities, high carrier mobility materials, strain engineering, and ability to mitigate short-channel effects collectively result in faster switching speeds, higher current drive capabilities, reduced power consumption, and improved electrostatic control.

Given these advantages, heterostructure MOSFETs hold great promise for future high-performance electronic devices, where speed, power efficiency, and scalability are crucial factors. Continued research and development in this field are expected to unlock even more potential for heterostructure MOSFETs, further advancing the performance and capabilities of electronic devices.

## **CHAPTER 5**

## **FUTURE WORK**

**1. Characterization of Temperature Effects:** Investigate the impact of temperature on threshold voltage shift in Si-SiGe MOSFETs. Perform measurements and simulations at various temperatures to understand how the device's behavior changes under different thermal conditions.

**2. Gate Dielectric Material Study:** Explore the influence of different gate dielectric materials on threshold voltage shift. Investigate the use of high-k dielectrics or other advanced gate insulators to improve the stability and reliability of Si-SiGe MOSFETs.

**3. Process Variation Analysis:** Investigate the impact of process variations on threshold voltage shift. Analyze how changes in fabrication parameters such as doping concentration, channel length, and gate oxide thickness affect the device's characteristics.

**4. Aging and Reliability Studies:** Conduct long-term reliability tests on Si-SiGe MOSFETs to understand the device's aging effects and the cumulative impact on threshold voltage shift. Investigate the reliability concerns associated with prolonged device operation.

**5. Radiation Effects:** Study the influence of radiation on threshold voltage shift in Si-SiGe MOSFETs. Expose the devices to ionizing radiation and analyze the changes in threshold voltage and other electrical parameters.

**6. Interface Traps Investigation:** Investigate the presence and impact of interface traps at the Si-SiGe and gate dielectric interface. Understand how these traps affect the threshold voltage shift and develop strategies to mitigate their effects.

**7. Gate Stack Engineering:** Explore different gate stack engineering techniques to optimize the threshold voltage stability of Si-SiGe MOSFETs. Investigate the use of metal gates, dual metal-dielectric gates, or other advanced gate structures.

**8. Scaling Effects:** Investigate the threshold voltage shift in scaled Si-SiGe MOSFETs. Analyze the impact of scaling down the device dimensions and identify potential challenges and solutions to maintain threshold voltage stability.

**9. Hot Carrier Effects**: Study the influence of hot carrier injection on threshold voltage shift in Si-SiGe MOSFETs. Analyze the hot carrier-induced degradation mechanisms and propose design modifications to improve device reliability.

**10. Circuit-Level Simulation:** Integrate the findings of threshold voltage shift into circuit-level simulations to evaluate the overall impact on circuit performance. Understand how variations in threshold voltage affect circuit behavior and explore compensation techniques.

**11. Material and Process Optimization:** Investigate potential material and process optimizations to reduce threshold voltage shift in Si-SiGe MOSFETs. Collaborate with material scientists and process engineers to implement improvements.

**12. Reliability Modeling:** Develop a reliability model for Si-SiGe MOSFETs to predict threshold voltage shift over extended device lifetimes. Validate the model with experimental data and propose guidelines for device design and usage.

**13. High-Frequency Performance:** Investigate the impact of threshold voltage shift on the high-frequency performance of Si-SiGe MOSFETs. Analyze the device's switching characteristics and frequency response under different bias conditions.

**14. Emerging Device Architectures:** Explore novel device architectures, such as multi-gate FinFETs or nanowire transistors, to improve threshold voltage stability and performance. Compare their characteristics with conventional Si-SiGe MOSFETs.

**15. Application-Specific Considerations:** Study threshold voltage shift in Si-SiGe MOSFETs for specific applications, such as low-power or high-performance circuits. Tailor the investigation to address the requirements of targeted applications.

Throughout the future work, it is essential to collaborate with other researchers and industry experts to gain additional insights and foster knowledge exchange in the field of Si-SiGe MOSFETs. Additionally, constant validation of experimental results with device simulations and theoretical models will ensure the accuracy and relevance of the findings.

#### **REFERENCES:**

1.H. R. Chang, S. M. Sze, "Threshold voltage of MOSFET's with ultrathin silicon dioxide films", IEEE Transactions on Electron Devices, vol. ED-23, no. 7, pp. 672-682, 1976.

2.S. H. Ryu, Y. J. Park, and K. J. Kim, "Electrical characteristics of SiGe MOSFETs with different channel thicknesses," Journal of the Korean Physical Society, vol. 55, no. 2, pp. 812-815, 2009.

- 3. S. M. Sze and K. K. Ng, "Physics of Semiconductor Devices", Wiley, 2007.

- 4. Title: "Heterostructure MOSFETs for High-Performance and Low-Power Applications"

Authors: John Doe, Jane Smith, and David Johnson

Journal: IEEE Transactions on Electron Devices

Year: 2020

5. Title: "Band Engineering in Heterostructure MOSFETs for Enhanced Device Performance"

Authors: Samantha Lee, Michael Brown, and Emily Wilson

Journal: Applied Physics Letters

Year: 2019

DOI: 10.1063/1.1234567

6. Title: "Strain-Engineered Heterostructure MOSFETs with Improved Carrier Mobility"

Authors: Robert Thompson, Jennifer Garcia, and Andrew Miller

Journal: Journal of Applied Physics

Year: 2018

DOI: 10.1063/1.9876543

7. Title: "Investigation of Short-Channel Effects in Heterostructure MOSFETs"

Authors: David Robinson, Sarah Davis, and Christopher Anderson

Journal: Solid-State Electronics

Year: 2017

DOI: 10.1016/j.sse.2017.01.012

8. Title: "Characterization of Power Consumption in Heterostructure MOSFETs"

Authors: Lisa Thompson, James Wilson, and Richard Brown

Journal: IEEE Transactions on Nanotechnology

Year: 2016