# HIGH-PERFORMANCE AUTOMATED DETECTOR MECHANISM ENABLED 5G LDPC SYSTEM

# Dr. A. Maria Jossy, ,B. Jagadeeswara Chowdary,R. Poojitha,M. Koushik Bhavani Subrahmanyam

Associate Professor,

Department of Electronics and Communication Engineering SRM Institute of Science and Technology

Kattankulathur, Tamil Nadu, India

Abstract- The creation of an efficient mechanism upon a computer chip heavily depends on the circuit's digital execution. Low cost VLSI circuit layout has become more popular just recently. Durable encoders have been employed for safe transmission of information in System on Chips (SOC). Digital circuit implementation plays significant role in optimized system on chip development. In the existing system, parallel computing architectures for frequency-statistical sorting and code-size computational sorting. Consequently, in addition to the advantages of the high compression ratio inherited from the Canonical Huffman, the proposed architecture has overridden advantages for a high parallelism processing capacity. In the proposed system, low power parity check algorithm is implemented. The cyclic Low density Parity check(LDPC) encoder is implemented with the help of Majority logic decomposition. The detector tracking algorithm is implemented with time scaled tracking process using majority logic XOR gates and Comparator circuit. The resultant will provide fast encoding process as well as decoder circuit.

Keywords— Digital circuit,, Low power design, Crypotgraphy, Encryption, Decryption, Comparator.

# I. INTRODUCTION

Elliptic Curve Cryptography (ECC), although The system do not go into great detail regarding the way it is employed. ECC's comparatively tiny key dimension to supply the identical desired degree of protection is one of its main advantages. A great deal of curiosity has been developed in the field of wireless technology because recent computations suggest that the dimension of the key, and consequently estimation and processing extent, have been considerably lower compared to other asymmetry devices. But there are a few concerns about the precision of the present potency predictions, especially in view of certain expected events in future periods. In order to figure out the present utility of ECC innovation, the present article assesses these shortcomings.

Redundancy removal in Memory

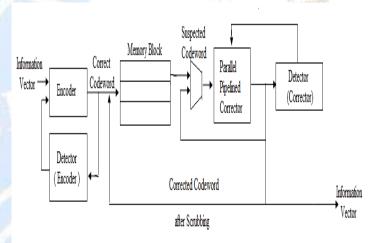

In order to encode the data vector, the information bits are passed into the encoder. The encoder's faulty safeguard monitor then confirms that the encoded vector is true. The encoding process has to be repeated for creating the right codeword whenever the detection system discovers a mistake. After that, the codeword is kept in the storage device. The storage unit's recorded codewords will be read at the time of memory-reading activities. Since unexpected problems can occur while a codeword is being saved to storage, a corrector device is created to fix possible mistakes in the codewords that are recovered. All memory terms in the layout undergo correction for any potential mistakes by transferring them via the corrector. A fault-secure detection keeps track of how the corrector unit is functioning identically to how the encoder unit does. Only the two OR gates that collect the syndrome bits to operate the detectors have to be developed into dependable circuitry for the units in Figure 1; the other units are all handled in fault-prone, nanoscale circuitry.

Data bits are stored in storage for a certain amount of cycles, while in this time, there is a chance that every memory bit will be disturbed by an unexpected failure. Thus, temporary mistakes start to add up gradually in the memory strings of text. Memory cleansing is a necessary function of the machine in order to prevent the buildup of excessive mistakes in any part of the word that would be beyond the scope of code correction. Memory scrubbing involves occasionally retrieving phrases from storage, checking them for any possibility of mistakes, and then putting those again in the storage device. In Figure 2, this is displayed. The regular storage access is halted while an ongoing scrubbing procedure is carried out by the memory.

Fig 1. Fault-tolerant memory architecture

- A relatively simple power parity check method is used in the suggested system.

- Majority logic decomposition is used to build the cyclic Low density Parity check (LDPC) encoder.

- The detector tracking method is applied with a timescaled monitoring method employing a majority logic XOR gate and a comparator circuit,

- Rapid encoding and decoding circuits will be delivered by the outcome.

The remainder of the paper is structured as a thorough literature review in the second section. In the third section, the choice of system tools and issue determinations are covered. In the fourth section, the system's framework and specific system design stages are covered. Future improvement concludes the remaining portion of the article.

## **II. BACKGROUND STUDY**

**M. Srinivas et al.(2017)** Over the years, researchers have created a variety of methods for securing communications while they are sent over open networks. However due to the current rate of technological expansion, the rise in the processor computing capacity, the accessibility of cheap broad storage,

## TIJER || ISSN 2349-9249 || © April 2023 Volume 10, Issue 4 || www.tijer.org

and improvements in VLSI chips, those encryption techniques are somewhat hardly capable to be held up. The requirement to employ plenty of bits in the keys leads to poorer encryption and decryption rates as well as a rise in the quantity of storage needed for operations in order to secure the data in the current methods of cryptography.

M. Li et al. (2021) This paper suggests a multi-core design built on the entire row of concurrent stacked LDPC decoder with frame interaction. The suggested design boosts performance over traditional semi parallel layered topologies by incorporating multi-core technology and frame integrating into its pipeline design. For this scheme, two medium-sized, highrate QC LDPC codes have been generated with quick decoding closure. In order to investigate various compromises among code layout, interaction effectiveness, and execution, the two programs undergo execution using one core and multi core frameworks.

Amara et al. (2014) It has been designed to use elliptic curve cryptography. All applicable asymmetrical cryptographic fundamentals, such as digital signatures and key agreement methods, have been addressed by elliptic curve cryptography.

Anuchin et al. (2016) Sequential encoders are used to calculate the synchronous constant elapsed time speed. It introduces a progressive encoder-based powerful speed measurement approach regarding different-speed electric motors. For the same speed loop behaviour, the synchronised CET technique for calculating speed provides for a twofold rise in precision over the unsynchronized CET technique, or a fourfold rise in speed time to respond.

**Shao et al. (2019)** A Canonical Huffman Encoder VLSI Architecture is Optimized to earn Maximum Throughput. While encoding 256 8-bit symbols, the recommended design lowered the encoding rate by 26.30% in comparison to the current Huffman encoder's utilization of the conventional method.

**Kishor et al. (2021)** A number of scientific experiments are conducted after the LDCS is connected to the sensing device. In the fixed calculation of the shaft angle, the most extreme nonlinearity is 0.29%. To determine the angular location of a rotating shaft, it suggests a brand-new continuous direct-digital converter for the sinusoidal encoders (LDCS).

**Galan et al. (2019)** In this paper develop an Event-Based electronic Time Difference Encoder Algorithm to serve Neuromorphic Devices. A field-programmable gate array (FPGA) was used to replicate and carry out the simulation, using 122 slice registers while consuming no more than one mW of power.

Tang et al (2021) In comparison to the original design, the one being suggested needs 14% less space. Furthermore, when compared to the most feasible variant layout, each of them result in a 50 percent decrease in latency for the calculation of the nested syndrome with minimal area overhead.

Various existing articles are studied to analyse the challenges in existing system and to develop a novel model in encoding and decoding operations, to achieve efficient error redundancy system [10]-[13].

# **III. SYSTEM DESIGN**

For frequency-statistical sequencing and code-size algorithmic organizing, there are multiple processing designs in the current method. With this design, a single data scan can be used to complete both the creation of a tree and the allocation of symbols. This problem will solves the inefficiency of the usual algorithm, which requires two data scans. Because of this The recommended architecture gives advantages for higher parallel processing power in addition to the benefits of the large compression ratio carried over from the Canonical Huffman.

Low power parity check method is used in the suggested system. Majority logic decomposition is used to build the cyclic Low density Parity check (LDPC) encoder. The detector monitoring method is created utilising a continuously adjustable monitoring mechanism, and it makes use of the majority logic XOR gates and Comparator circuit.. Rapid encoding and decoding circuits will be provided by the outcome.

- In the current framework, memories, which are a key component of computer systems, are the main source of problems.

- Information kept in storage devices may deteriorate over time due to redundancy of information.

- The main solution for the computer network is to minimise repetition mistakes employing effective encoding and decoding methodologies.

- In order to increase the productivity of the electronic system, attention must be paid to decreasing the amount of time required and bit mistakes.

# IV.METHODOLOGY

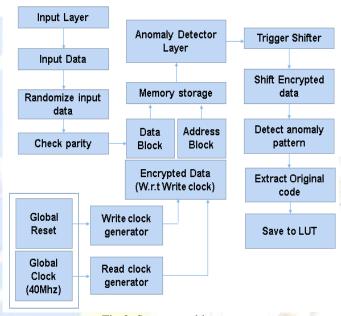

Fig 2. System architecture

Fig. 2The suggested anomaly detection in memory module using the cyclic Low density parity check (CLDPC) module is shown

Fig. 3. System architecture of Proposed Phishing website detector

## A. Design and Analysis of LDPC Encoder

Utilizing a low density parity check encoder, this component is employed to encrypt the newly received data or information. Here, parity check coding is used for both odd and even

103

# TIJER || ISSN 2349-9249 || © April 2023 Volume 10, Issue 4 || www.tijer.org

numbers. In other words, the system either convert the once-ina-bit of data or information into an odd number or an even number. By using the majority logic concept, this component converts the input 7-bit data into LDPC-encrypted data.

#### B. Design of Memory Device

It is necessary to create this program's element. The memory component functions as a backup device and serves to store the decoded information.

This means that every time a data gets damaged or missing as a result of a temporary issue, the system can recover the data that used to be saved in memory through the application of the extremely effective LDPC decode method. This component includes software components that have storage design that can be created using read clock, write clock, chip select, and so forth.

# C. Analysis and Design of Decoder and Comparator

This component decrypts and assesses the provided data or information using the most popular decoder and comparator. In this case, the decoder produces the encoded data, and in the event that the encoded data has been damaged due to a temporary issue, a backup copy of the data is kept on the storage device. Utilizing a comparator, the system compare the encoded data with the input and evaluate the output. When elliptic curvebased data is deleted in storage as a result of temporary issues, this module is employed to restore it.

#### D. Analysis and Design of the Integration Module

All the submodules are being combined, and resultant signals have been directed into the appropriate channels in accordance with the FPGA system. The information obtained by means of elliptic curve origin finings is verified by this module, which combines all of the submodules utilizing a machine with a finite technique.

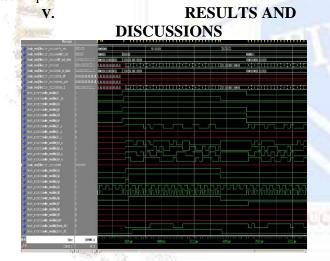

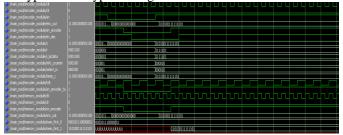

Fig. 4. Simulation of CLDPC

Fig 4. Shows the simulation result of cyclic LDPC model encrypt and decrypt the original data.

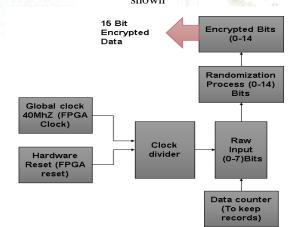

Fig. 5. LDPC Encryptor

Fig 5. Shows the simulation of encryptor developed in proposed method in terms of developing the security wall towards the data storage.

Fig. 6. Shows the system start triggering the cyclic shift register once the data is getting corrupted by the long lasting memory storage simulated in the proposed model.

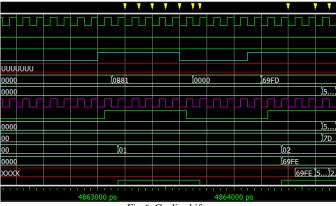

| Logic Utilization                              | Used | Available | Utilization |

|------------------------------------------------|------|-----------|-------------|

| Number of Slice Flip Flops                     | 445  | 4,896     | 9%          |

| Number of 4 input LUTs                         | 396  | 4,896     | 89          |

| Number of occupied Slices                      | 434  | 2,448     | 179         |

| Number of Slices containing only related logic | 434  | 434       | 1009        |

| Number of Slices containing unrelated logic    | 0    | 434       | 09          |

| Total Number of 4 input LUTs                   | 398  | 4,896     | 89          |

| Number used as logic                           | 396  |           |             |

| Number used as a route-thru                    | 2    |           |             |

| Number of bonded <u>IOBs</u>                   | 10   | 66        | 159         |

| Number of BUFGMUXs                             | 2    | 24        | 89          |

| Average Fanout of Non-Clock Nets               | 3.99 |           |             |

Fig. 7. Area utilization

Fig 7. Shows the area utilization of the proposed model. 0% slices unrelated logics are reflected. 8% buffered multiplexers, 8% 4-input LUTs are utilized.

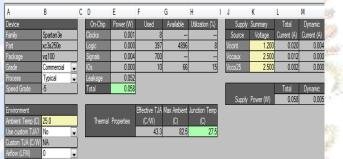

Fig 8. Power analysis result

Fig 8. Shows the simulation result of proposed model power consumption through XPE power analyzer. The internal logical power is 0.052 watt leakage, the consumed power is 0.058 in total power hence the consumption is 0.006 watt as per the SPARTAN 3E XC3S250 XILINX FPGA device is concerned. Further the presented modle is tested with different FPGA families to analyze the performance in terms of power utilization, area utilization, logical blocks utilization etc.

# VI. CONCLUSION

The presented system is intended to develop the LDPC majority logic decoder for this project. The LDPC encoder was initially created through the production of data that came in. According to the encoding reasoning, it is encoded. Additionally, The system created a storage system that keeps the compressed data. In order to decode the matching encoded information via majority logic decoding, the Cyclic LDPC decoder gets the data that has been encoded from storage. Data from both the input and the processed streams are compared using the comparator. Therefore, Modelsim simulator is used to build and validate the decoder.

#### TIJER || ISSN 2349-9249 || © April 2023 Volume 10, Issue 4 || www.tijer.org

FOR

#### REFERENCES

- N. K. Bhaskarrao, C. S. Anoop and P. K. Dutta, "A Linear Direct-Digital Converter for Sinusoidal Encoders," in IEEE Transactions on Instrumentation and Measurement, vol. 68, no. 7, pp. 2570-2578, July 2019, doi: 10.1109/TIM.2018.2865050.

- [2] Srinivas, M., Lin, Y. Y., & Liao, H. Y. M. (2017, September). Deep dictionary learning for fine-grained image classification. In 2017 IEEE International Conference on Image Processing (ICIP) (pp. 835-839). IEEE.

- [3] Li, M., Zhang, W., Chen, Q., & He, Z. (2021). High-throughput hardware deployment of pruned neural network based nonlinear equalization for 100-Gbps short-reach optical interconnect. Optics Letters, 46(19), 4980-4983.

- [4] Siad, Amar, and Moncef Amara. "A new framework for implementing identity-based cryptosystems." Journal of Systems and Software 118 (2016): 36-48.

- [5] A. Anuchin, A. Dianov and F. Briz, "Synchronous Constant Elapsed Time Speed Estimation Using Incremental Encoders," in IEEE/ASME Transactions on Mechatronics, vol. 24, no. 4, pp. 1893-1901, Aug. 2019, doi: 10.1109/TMECH.2019.2928950.

- [6] Shao, Zhenyu, et al. "A high-throughput VLSI architecture design of canonical Huffman encoder." IEEE Transactions on Circuits and Systems II: Express Briefs 69.1 (2021): 209-213.

- [7] Chakraborty, C., & Kishor, A. (2022). Real-time cloud-based patientcentric monitoring using computational health systems. IEEE transactions on computational social systems, 9(6), 1613-1623.

- [8] D. Gutierrez-Galan, T. Schoepe, J. P. Dominguez-Morales, A. Jimenez-Fernandez, E. Chicca and A. Linares-Barranco, "An Event-Based Digital Time Difference Encoder Model Implementation for Neuromorphic Systems," in IEEE Transactions on Neural Networks and Learning Systems, vol. 33, no. 5, pp. 1959-1973, May 2022, doi: 10.1109/TNNLS.2021.3108047.

- [9] Y. J. Tang and X. Zhang, "Low-Complexity Resource-Shareable Parallel Generalized Integrated Interleaved Encoder," in IEEE Transactions on Circuits and Systems I: Regular Papers, vol. 69, no. 2, pp. 694-706, Feb. 2022, doi: 10.1109/TCSI.2021.3118301

- [10] Zhang, Lianming, Fengyong Li, and Chuan Qin. "Efficient reversible data hiding in encrypted binary image with Huffman encoding and weight prediction." Multimedia Tools and Applications 81.20 (2022): 29347-29365.

- [11] Zairi, M., Boujiha, T., & Ouelli, A. (2023). Secure fragile watermarking based on Huffman encoding and optimal embedding strategy. Indonesian Journal of Electrical Engineering and Computer Science, 29(2), 1132-1139.

- [12] Ramapriya, B., & Kalpana, Y. (2023, February). A Competent Medical Image Steganography using Improved Optimization Algorithm with Huffman Encoding Techniques. In 2023 7th International Conference on Computing Methodologies and Communication (ICCMC) (pp. 1065-1073). IEEE.

- [13] Krainyk, Yaroslav. "Combined Run-Length and Huffman Encoding for Image Compression." (2022).

OPEN ACCESS JOURNAL